中科院微电子所先导中心朱慧珑研究员课题组–世界上首个具有自对准栅极的叠层垂直纳米环栅晶体管的实现

从Intel首发22nm FinFET工艺之后,全球主要的半导体厂商在22/16/14nm节点开始启用FinFET鳍式晶体管,目前全球最先进的半导体工艺已经进入7nm,下一步还要进入5nm、3nm节点,制造难度越来越大,其中晶体管结构的限制至关重要,未来的工艺需要新型晶体管。三星在去年率先宣布3nm节点改用GAA环绕栅极晶体管。基于全新的GAA晶体管结构,三星通过使用纳米片设备制造出了MBCFET(Multi-Bridge-Channel FET,多桥-通道场效应管),该技术可以显著增强晶体管性能,主要取代FinFET晶体管技术。

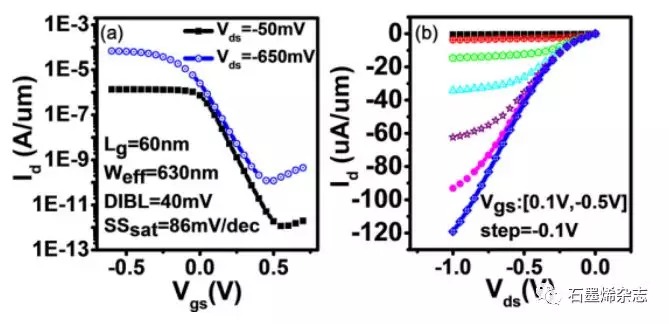

基于上述信息也可以看出GAA环绕栅极晶体管的重要意义。这里,朱慧珑课题组系统地研发了一种原子层选择性刻蚀锗硅的方法,结合多层外延生长技术将此方法用于锗硅/硅超晶格叠层的选择性刻蚀,从而精确地控制纳米晶体管沟道尺寸和有效栅长,首次实现了垂直纳米环栅晶体管的自对准高k金属栅后栅工艺。其集成工艺与主流先进CMOS制程兼容。所获得的栅长约60 nm,纳米片厚度20 nm的p型VSAFET。原型器件的SS、DIBL和电流开关比(Ion/Ioff)分别为86 mV/dec、40 mV和1.8×105。

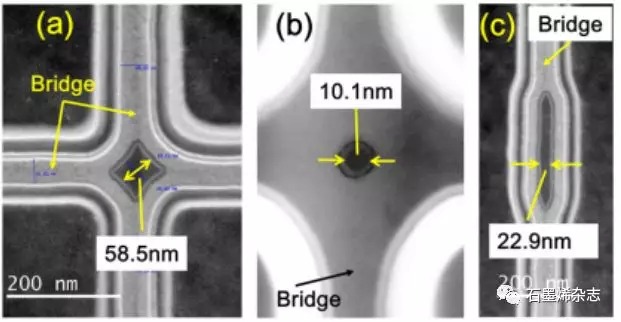

Figure 1. VSAFETs的工艺流程。(a)Si/SiGe/Si之后的SEM图,(b)RIE之后的3D结构SEM图,(c)qALE之后的SEM图,(d)HKMG沉积后的TEM图。

Figure 2. VSAFETs的原理示意图。(a)单个装置的结构设计,(b)两个装置串联连接的的测试结构。

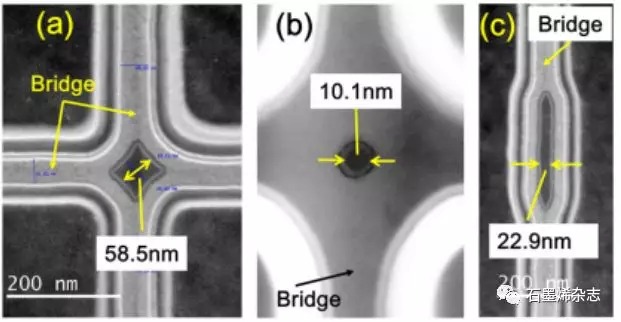

Figure 3. 配有包覆HKMG的VSAFETs的STEM顶视图。(a)方形横截面纳米线,(b)圆形横截面纳米线,(c)纳米片。

Figure 4.栅极金属在活性离子刻蚀后(RIE),(a)VSAFETs的SEM图:纳米片装置的HKMG和(b)与栅极的局部连接。

Figure 5.(a)pVSAFETs器件的结构和I-V特性,(a)转移特性曲线和(b)输出特性曲线。

该研究工作由中科院微电子所先导中心朱慧珑研究员课题组于2019年发表在国际微电子器件领域的顶级期刊《IEEE Electron Device Letters》上。原文:Vertical Sandwich Gate-All-Around Field-Effect Transistors with Self-Aligned High-k Metal Gates and Small Effective-Gate-Length Variatio(DOI: 10.1109/LED.2019.2954537)

本文来自石墨烯资讯,本文观点不代表利特纳米立场,转载请联系原作者。